#### Parallel Interface

- Parallel ports and LCD

- DC Motor and Relay

- Stepper motor

- Camera

- ISA Bus

- PCI Bus

- ARM Bus

- Other buses

#### Parallel port

• Multi-bit I/O

• Short distances

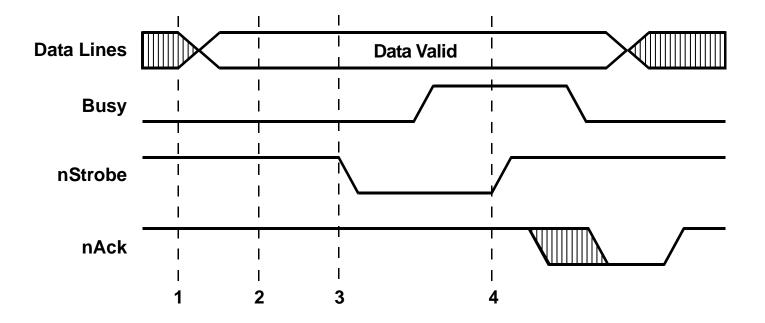

# Parallel Port transfer of an 8-bit data value to a printer

# **Parallel Printer I/O Operation**

- 1. Computer waits for port's output ready bit (i.e. busy=0)

- 2. Computer outputs a new 8-bit data value

- 3. Computer toggles strobe control line

- 4. Computer must wait for ack to pulse low before any data or strobe line changes

- Printer can be busy for long time periods (out of paper, offline, page feed...etc)

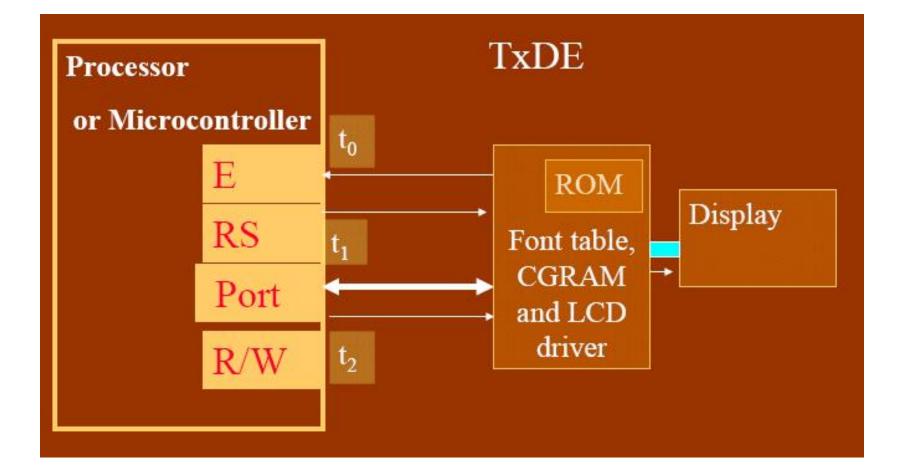

#### LCD controller interface

# LCD

- RS is reset signal

- E is enable bit

There is an interval in which controller maybe in disable state such as clear display (e.g., takes 150  $\mu$ s)

- Port- 8 bit parallel port for control/data bus

(RS = 0 control/RS =1 data)

- R/W' = read or write port

- LCD controller has M display characters stored in ROM

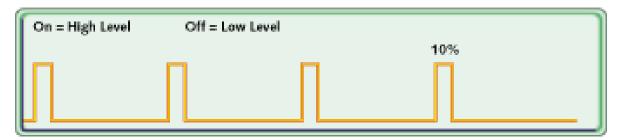

# Pulse Width Modulation (PWM)

- PWM is a way for controlling analog circuits with digital output

- By controlling analog circuit digitally, system cost and power consumption can be reduced

- Used in audio, motor control, telecommunication

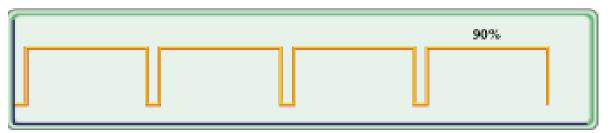

- The duty cycle is the proportional of the on time to the regular interval or period

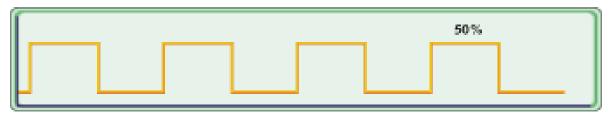

# PWM with 10%, 50%, and 90% duty cycle

## **PWM Signal**

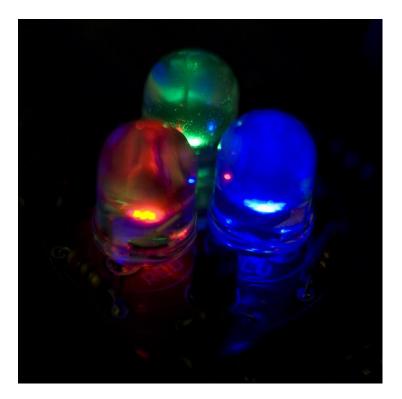

## **PWM Applications**

- LED light control

- Motor speed

- Acoustics sound

## PWM in RaspberryPi

Two software modules are available:

- RPI.GPIO is http://sourceforge.net/projects/raspberrygpio-python

- RPIO is available from http:///pythonhosted.org/RPIO

#### **GPIO** Function in RPIO

| Function                                                                                                                                                               | Description                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| <pre>setmode(int num_mode)</pre>                                                                                                                                       | Identifies the method of pin numbering                                                              |

| <pre>setup(int pin, int mode)</pre>                                                                                                                                    | Configures a pin as an input or output                                                              |

| <pre>setup(int pin, int mode,</pre>                                                                                                                                    | Configures a pin as an input or output, and con-<br>nects a pull-up or pull-down resistor           |

| output(int pin, int level)                                                                                                                                             | Sets a pin's logic level to RPIO.HIGH or RPIO.LOW                                                   |

| int input (int pin)                                                                                                                                                    | Reads the logic level at the given pin                                                              |

| cleanup()                                                                                                                                                              | Sets pins to default state                                                                          |

| <pre>add_interrupt_callback   (int pin, callback_func,     edge='both',     pull_up_down=RPIO.PUD_OFF,     threaded_callback=False     debounce_timeout_ms=None)</pre> | Associates a callback function with the given pin<br>and an event that meets the specified criteria |

| <pre>wait_for_interrupts    (threaded=False,         poll_timeout=1)</pre>                                                                                             | Halts processing until an interrupt occurs                                                          |

| del_interrupt_callback<br>(int pin)                                                                                                                                    | Used to remove callbacks associated with the pin                                                    |

#### **RPIO Code Example:**

import RPIO

# Set input pins

in\_pin = 17;

out\_pin = 24;

# Specify use of BCM pin numbering

RPIO.setmode(RPIO.BCM)

# Configure pin directions RPIO.setup(in\_pin, RPIO.IN) RPIO.setup(out\_pin, RPIO.OUT)

# Wait for in\_pin to reach low voltage while(RPIO.input(in\_pin) == RPIO.LOW): RPIO.output(out\_pin, RPIO.HIGH)

# Return pins to default state RPIO.cleanup()

#### **RPIO Code with Interrupt**

import RPIO

def edge\_detector(pin\_num, rising\_edge):

if rising\_edge:

print("Rising edge detected on Pin %s" % pin\_num) else:

print("Falling edge detected on Pin %s" % pin\_num)

in\_pin = 17 RPIO.setmode(RPIO.BCM) RPIO.setup(in\_pin, RPIO.IN)

# Configure interrupt handling for rising and falling edges RPIO.add\_interrupt\_callback(in\_pin, edge\_detector, edge='both') RPIO.wait\_for\_interrupts()

RPIO.del\_interrupt\_callback(in\_pin) RPIO.cleanup

#### **RPIO.PWM Module**

| Function                                                                 | Description                                                    |

|--------------------------------------------------------------------------|----------------------------------------------------------------|

| <pre>setup(pulse_incr_us=10,     delay_hw=0)</pre>                       | Initializes the DMA channels for use                           |

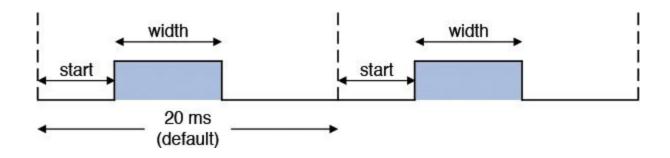

| <pre>init_channel(int dma_channel,     subcycle_time_us=20000)</pre>     | Configures the cycle with a specific period (20 ms by default) |

| add_channel_pulse<br>(int dma_channel, int pin,<br>int start, int width) | Generates pulse of the given width for the pin                 |

| clear_channel<br>(int dma_channel)                                       | Clears all pulses from the channel                             |

| <pre>clear_channel_gpio   (int dma_channel, int pin)</pre>               | Clears the pulse for the specified pin from the channel        |

| cleanup()                                                                | Halts PWM and DMA                                              |

#### **PWM Control with RPIO**

#### **RPIO Code with PWM**

import RPIO.PWM as PWM import time

# Define PWM pin pwm\_pin = 18

# Initialize DMA and set pulse width resolution PWM.setup(1)

```

# Initialize DMA channel 0

PWM.init_channel(0)

```

# Set pulse width to 1000us = 1ms

PWM.add\_channel\_pulse(0, pwm\_pin, 0, 1000)

time.sleep(10)

# Clear DMA channel and return pins to default settings PWM.clear\_channel(0) PWM.cleanup()

#### **RPIO Servo motor**

import RPIO.PWM as PWM import time

servo\_pin = 18 min\_width = 700 max\_width = 2300

# Create servo object servo = PWM.Servo() # Set the angle to the minimum angle and wait servo.set\_servo(servo\_pin, min\_width) time.sleep(1) # Rotate shaft to maximum angle for angle in xrange(min\_width, max\_width, 100): servo.set\_servo(servo\_pin, angle) time.sleep(0.25)

#### **RPIO Servo motor**

# Rotate shaft to minimum angle for angle in xrange(max\_width, min\_width, -100): servo.set\_servo(servo\_pin, angle) time.sleep(0.5)

# Stop delivering PWM to servo servo.stop\_servo(servo\_pin

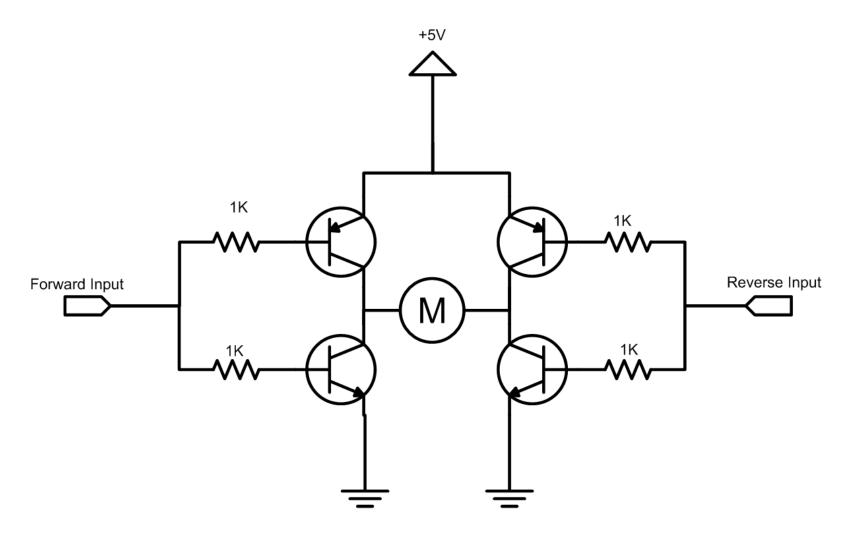

# **Driving Motors and Relays**

- High current devices like motors, relays, solenoids, buzzers, and light bulbs can require more than 500mA of current

- Even though voltage levels may be the same, digital outputs from a GPIO (parallel) port typically drive only 5-20mA of current

- They cannot drive high current devices directly and trying to do so will likely blow out the output circuit

# **Driver Circuits**

- A higher current driver circuit must be added after the digital output pin and before the device

- A driver circuit typically uses a discrete power transistor

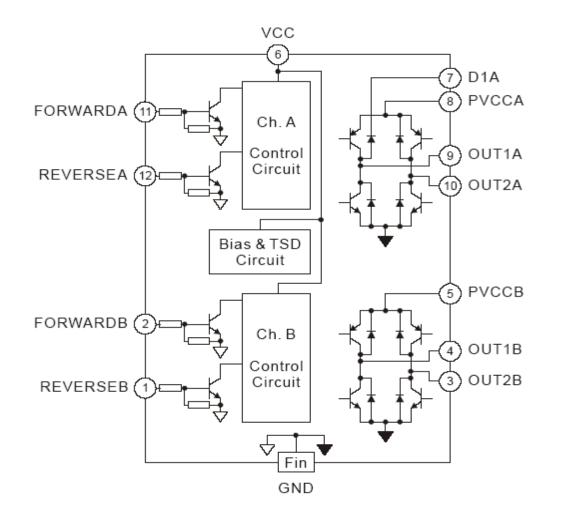

- For DC motors, consider using an H-bridge circuit module. It contains four power transistors than can also reverse the motor.

- Diodes are often used for additional protection across the load on motors and relays. When you turn off the current in an inductive load it generates a reverse voltage spike that might damage the transistor (back EMF). The diode shorts it out.

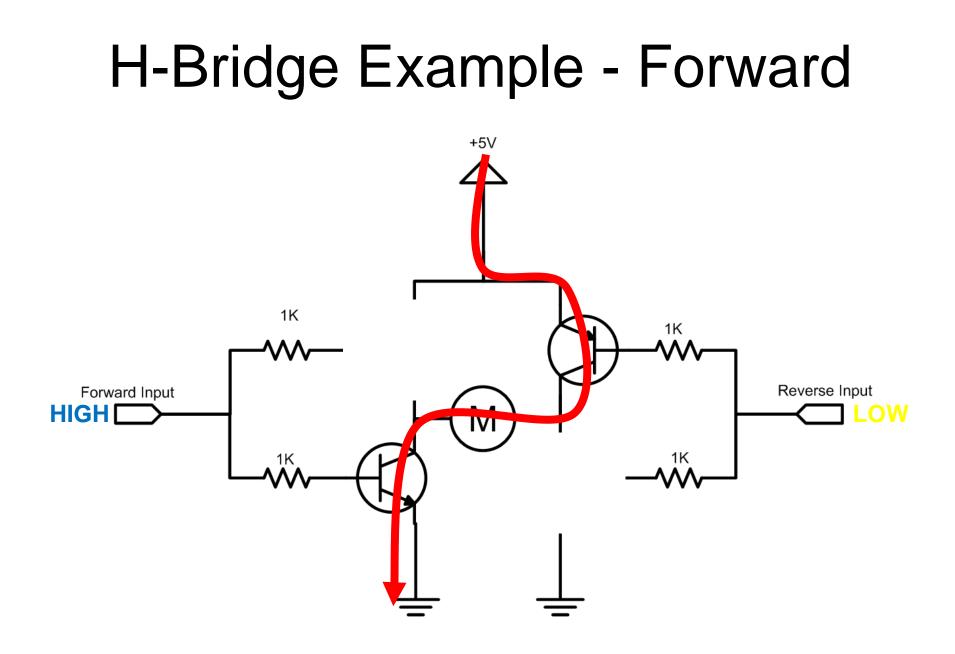

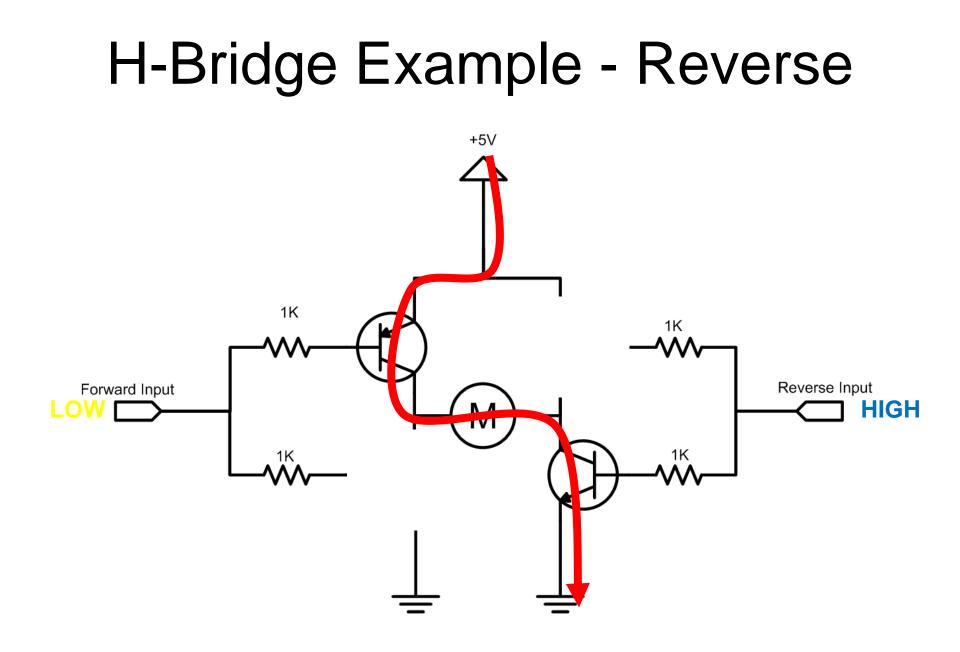

#### H-Bridge - DC Motor Driver Circuit

## **H-Bridge Control Functions**

| Input | Function                                          | Operation                                                 |

|-------|---------------------------------------------------|-----------------------------------------------------------|

| 10    | Forward                                           | DC Motor runs in the forward direction                    |

| 0 1   | Reverse                                           | DC Motor runs in the reverse direction                    |

| 0 0   | Stop                                              | Motor is not connected – Coasts                           |

| 11    | Brake* or<br>Short Power Supply<br>(not allowed!) | Motor Terminals<br>Shorted or<br>Power Supply<br>Shorted! |

\*The Brake function requires a more complex decoder circuit to control the power transistors. Check the H-Bridge data sheet to make sure it is supported before using it. In some simple H-Bridge circuits, the fourth state must be avoided (i.e., illegal state) and it will short out the power supply!

**Figure 3.10** Fairchild FAN8100N Low Voltage Dual H-Bridge DC Motor Driver IC. Images courtesy of Fairchild Semiconductor.

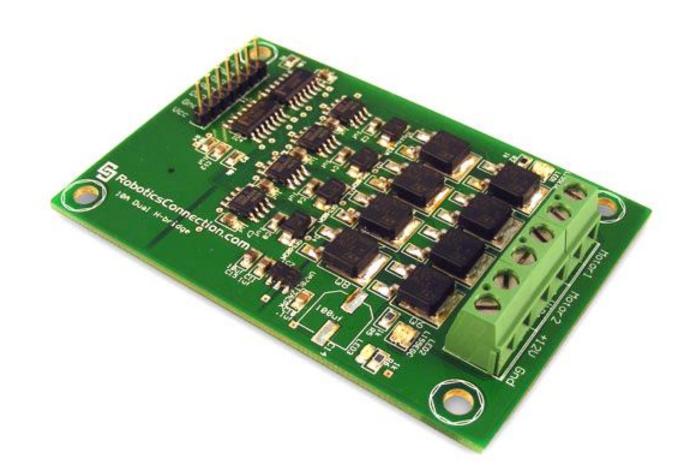

Higher current H-Bridge modules typically use discrete power transistors assembled on a board. This dual H-Bridge module switches up to 10 amps at 24V DC. The eight power transistors can be see arranged on the right side of the board. Photograph courtesy of RoboticsConnection.

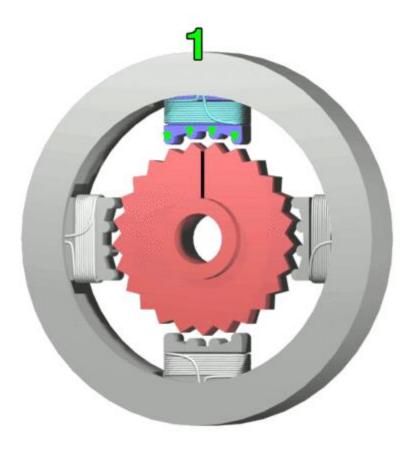

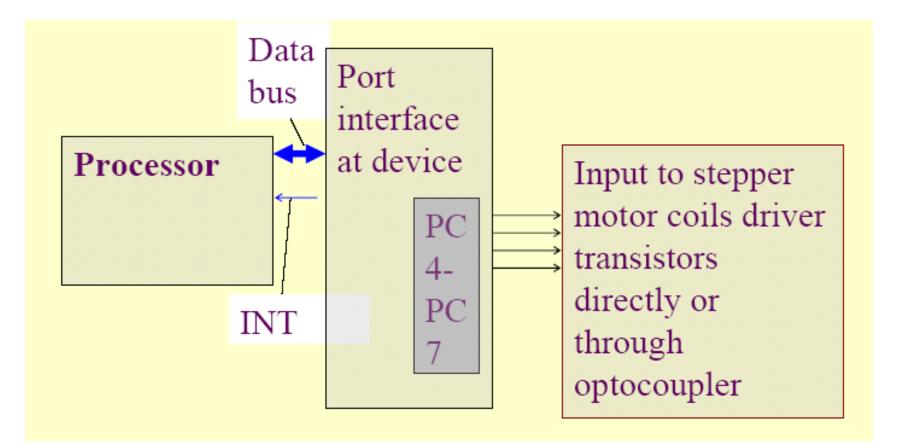

### Stepper motor

- A synchronous electric motor that can divide a full rotation into a number of steps

- Motor position can be controlled precisely without any feedback system

- Doesn't require feedback sensor

- Operate in DC power

- Used in many devices such as harddisk drives, and printers

- Can make motor spin by outputting the sequence like ... 10,9,5,6,10,9,5,6....

- For 200 steps motor, each new output will cause the motor to rotate 1.8 degree

#### Stepper motors

#### Stepper motor

## Raspberry pi Camera

Raspberry Pi can interface through:

- Camera Serial Interface (CSI)

- USB

- IP Camera

#### RasPi Camera modules

Raspberry Pi camera module: 5 M pixels at 30 FPS

Raspberry Pi camera module black NoIR

https://www.pyimagesearch.com/2017/09/04 /raspbian-stretch-install-opencv-3-pythonon-your-raspberry-pi/

sudo raspi-config

- enable SSH

- enable Camera

sudo apt-get update sudo apt-get upgrade sudo apt-get –y install synaptic

sudo apt-get -y install python-numpy pythonscipy python-nose python-pandas pythonmatplotlib ipython-notebook python-sympy

sudo apt-get -y install libgtkglext1-dev sudo apt-get -y install build-essential cmake pkg-config

sudo apt-get -y install qtcreator qt4-dev-tools libqt4-dev libqt4-core libqt4-gui v4l-utils

wget http://sourceforge.net/projects/opencvlibrary/ files/opencv-unix/2.4.10/opencv-2.4.10.zip unzip opencv-2.4.10.zip tar xzvf opencv-2.4.10.tar.gz cd opencv-2.4.10 mkdir build cd build

cmake -D CMAKE\_BUILD\_TYPE=RELEASE -D WITH\_OPENGL=ON -D INSTALL\_C\_EXAMPLES=ON -D INSTALL\_PYTHON\_EXAMPLES=ON -D WITH\_QT=ON -D CMAKE\_INSTALL\_PREFIX=/usr/local -D WITH\_TBB=ON -D WITH\_V4L=ON -D BUILD\_NEW\_PYTHON\_SUPPORT=ON -D BUILD\_EXAMPLES=ON

make sudo make install sudo nano /etc/ld.so.conf.d/opencv.conf add /usr/local/ib

sudo nano /etc/bash.bashrc

add

PKG\_CONFIG\_PATH=\$PKG\_CONFIG\_PATH:/usr/local/lib/pkgconfig export PKG\_CONFIG\_PATH

# Testing

Isusb # list all usb devices sudo apt-get –y install guvcview # capture image

Ixsession

guvcview

cd /home/pi/opencv-2.4.10/samples/python

S

python facedetect.py

### **OpenCV** Example

import cv2

img =

cv2.imread('/home/pi/screenshot.jpg',cv2.IMREAD\_GRAYSCALE)

cv2.imshow('image',img)

cv2.waitKey(0)

cv2.destroyAllWindows()

#### Result

# **Bus history**

- Industry System Architecture (ISA)

- Developed by IBM in 1981 for IBM XT (extended technology) 8 bits

- Modified for 16 bits for IBM AT (advance technology)

- Later, they rename AT bus to ISA bus

- IBM move to replace IBM AT bus with MCA (Micro Channel Architecture)

# **Bus history**

- Gang of nine IBM PC compatible manufacturers announces EISA to fight with MCA for 32 bits

- PCI (Peripheral Component Interface) is developed by Intel in 1990 (my exmanager was in that team)

- AGP Accelerated Graphics Port

- PCI-E (Express) is the extension of PCI

- ARM bus is designed for ARM architecture

#### A First Generation Bus Example: ISA

- ISA bus used in early PCs for Plug-in Cards

- Address Bus (SAx)

- Originally 16 bits then expanded to 24

- Data Bus (SD*x*)

- 8 bits then 16 bits

- EISA expanded it to 32 bits

- Bus Status Signals

- MEMR, MEMW, IOR, IOW

- 5V TTL signals

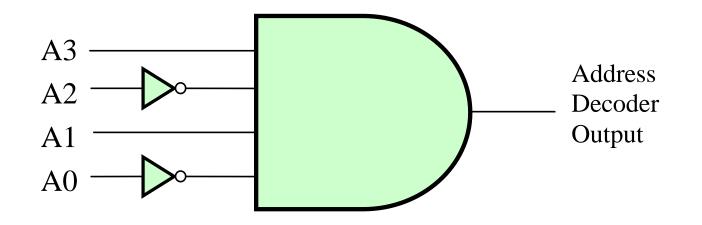

#### Digital Logic Review: A simple address decoder circuit for 4-bit address (A3..A0) = 0xA = 1010B

Would need to decode more address bits in an actual system

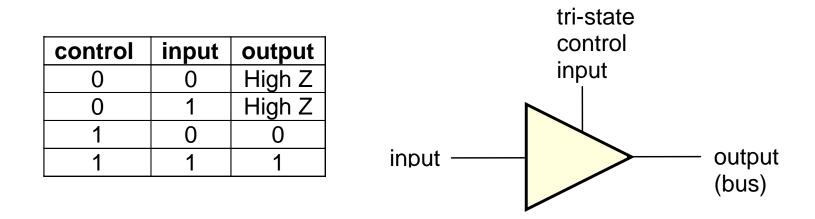

# Tri-state logic gate outputs are used to drive most bus signals

Hardware allows only one tri-state gate at a time to drive a bus signal!

Works just like a large multiplexer: One of several inputs connects to the output

#### Legacy PC I/O address assignments

| I/0 address range | I/O device                          |

|-------------------|-------------------------------------|

| 000h - 200h       | Reserved for Internal Devices:      |

|                   | Interrupt & DMA controllers, timers |

| 278h - 27Fh       | Parallel Printer (LPTx:)            |

| 2E8h - 2EFh       | Serial Port 4 (COM4:)               |

| 2F8h - 2FFh       | Serial Port 2 (COM2:)               |

| 378h - 37Fh       | Parallel Printer (LPT1:)            |

| 3B0h - 3BBh       | MDA Adapter                         |

| 3BCh - 3BFh       | Parallel Printer (LPTx:)            |

| 3C0h - 3CFh       | VGA/EGA Adapter                     |

| 3D0h - 3DFh       | CGA Adapter                         |

| 3E8h - 3EFh       | Serial Port 3 (COM3:)               |

| 3F0h - 3F7h       | Floppy Controller                   |

| 3F8h - 3FFh       | Serial Port 1 (COM1:)               |

Original PC design only decoded low 10 I/O address bits to save hardware

#### ISA bus

| ISA           |                |

|---------------|----------------|

| GND B1        | A O AT VOCHCK  |

| RESET DRV B2  | + A2 D7        |

| +54 83        | A3 06          |

| IRQ2 B4       | 5 A4 D5        |

| -5V 85        | TENIO AS DA    |

| DRQ 2 B6      | A6 03          |

| -12V B7       | A7 D2          |

| Reserviert B8 | AS DI          |

| +12V B9       | AS DO          |

| GND B10       | A 10 VO CH RDY |

| MEMW B11      | A11 AEN        |

| MEMR B12      | A12 A19        |

| IOW B13       | A13 A18        |

| IOR 814       | A14 A17        |

| DACK 3 B15    | A15 A16        |

| DRQ 3 816     | A16 A15        |

| DACK 1 B17    | A17 A14        |

| DRQ 1 B18     | A18 A13        |

| DACKO B19     | A19 A12        |

| CLK B20       | A20 A11        |

| IRQ 7 B21     | A21 A10        |

| IRQ 6 822     | A22 A9         |

| IRQ 5 823     | A23 A8         |

| IRQ 4 824     | A24 A7         |

| IRQ 3 825     | A25 A6         |

| DACK 2 B26    | A26 A5         |

| T/C 827       | A27 A4         |

| ALE 828       | A28 A3         |

| +5V B29       | A29 A2         |

| OSC B30       | A30 A1         |

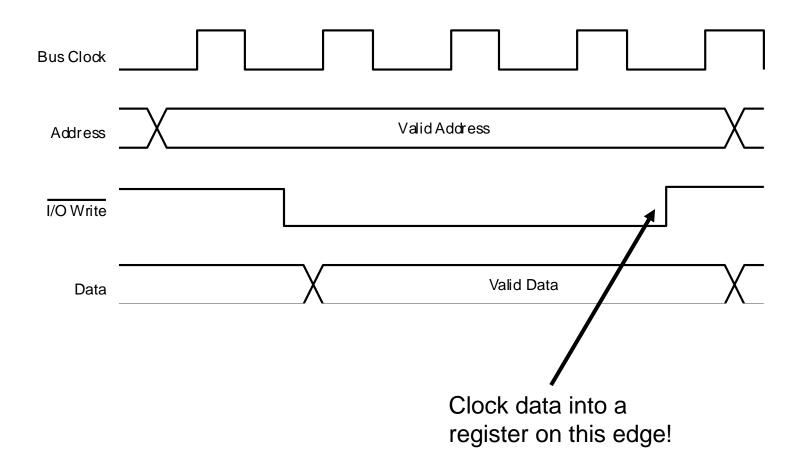

#### An Example ISA Bus I/O Write Operation

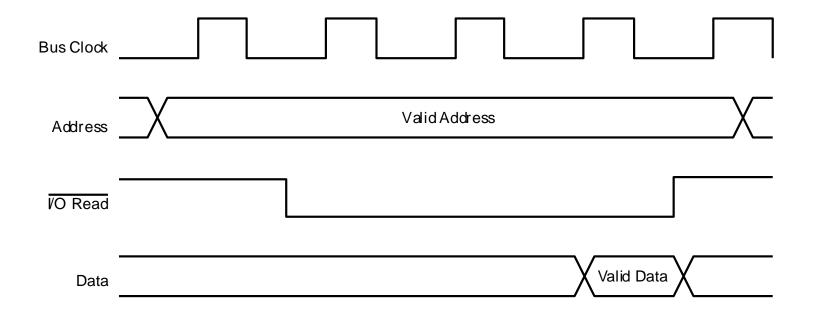

#### An Example ISA Bus I/O Read Operation

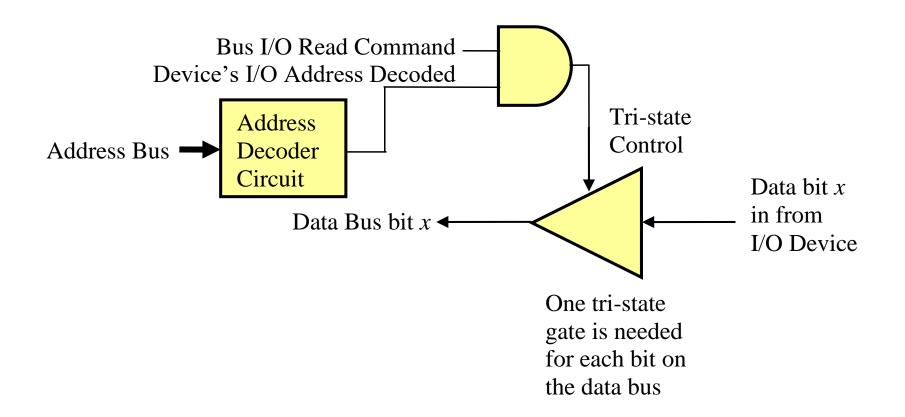

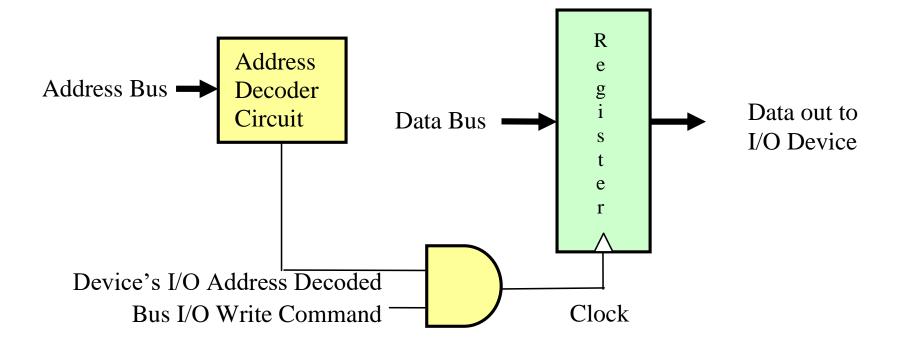

#### Typical I/O Input Port Hardware Operation

#### Typical I/O Output Port Hardware Operation

# Software for I/O port transfers

Can use in-line assembly language in C/C++

Most C/C++ compilers have built-in function calls for I/O port input and output

#### **In-line Assembly Example for X86**

| // I/O Input Routine |                       | // I/O Output Routine |                       |  |  |

|----------------------|-----------------------|-----------------------|-----------------------|--|--|

| asm{                 |                       | asm                   | {                     |  |  |

| mov                  | dx, <i>IO_address</i> | mov                   | dx, <i>IO_address</i> |  |  |

| in                   | al, dx                | mov                   | al, <i>IO_data</i>    |  |  |

| mov                  | <i>IO_data</i> ,al    | out                   | dx, al                |  |  |

| }                    |                       | }                     |                       |  |  |

**Problems:** Does not port to other processors and many people do not understand assembly language!

#### Windows CE C/C++ I/O Port R/W Functions

• **READ\_PORT\_UCHAR**(*I/O\_Address*)

- Returns 8-bit input value from port

• WRITE\_PORT\_UCHAR(I/O\_Address,I/O\_Data)

- Sends 8-bit data value to output port

- Found in CE Device Driver Kit (CEDDK)

- Need to link to CEDDK.lib library and include CEDDK.h – modify sources file for this

- Typically used in low-level device drivers

### A Second Generation Bus - PCI

- 32-bit Multiplexed Address and Data Bus (AD)

- Address sent on first clock cycle

- Bus command sent on first clock cycle (C/BE)

- Data on subsequent clock cycles

- Bus Clock rates 33 to 512Mhz

- One Data transfer per clock is possible

- Supports Data Bursts (example to follow)

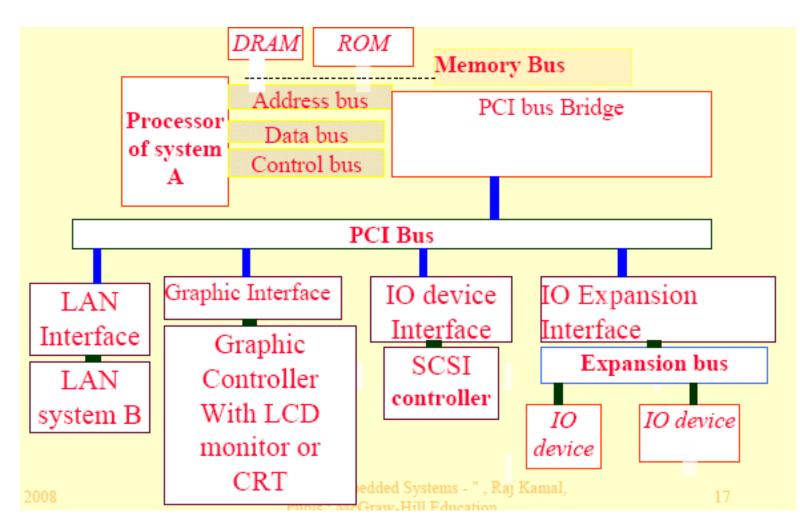

# Computer System PCI

- When I/O devices are distributed in the network, all can communicate through a common parallel bus

- PCI connects at high speed to other devices on a very short distances (<25 cm) using a parallel bus

# PCI bus applications

- Display monitor

- Printer

- Streaming displays

- Network subsystems

- Video card

- Digital video capture card

- Harddisk controller

## PCI bus features

- 32 bit data bus extendible to 64 bit

- Support both Synchronous and Asynchronous transfer

- Automatically detects the interfacing systems and assign new address

- Simplify the addition and deletion of the system peripherals

### Identification numbers

- A device identifies its address space by three identification numbers

- I/O port

- Memory locations

- Configuration registers

# Each PCI device has address space allocation of 256 bytes

### PCI device

- A 32-bit register in a PCI device for device ID and allow auto-detection

- Each device may use a FIFO controller with a FIFO buffer for maximum throughput

- Independent from IBM architecture

- Number of embedded devices use PCI bus

# PCI bridge

- PCI bridge switches the communication between memory bus to PCI bus

- In most systems, the processor has a single bus that connects to a PCI bridge

- Some processor integrates PCI bridge within the processor to reduce the system cost

# PCI bridge/switch

Another configuration:

• Separate memory bus

A separated I/O bus connected to PCI switch to the I/O devices

• Widely used in desktop PC

### PCI bridge and buses

## PCI

32 bit 33 MHz

throughput = <sup>133</sup> MBps

64 bit 66 Mhz

throughput = 533 MBps

#### PCI Bus Commands (C/BE)

| PCI Bus Command             | C/BE |

|-----------------------------|------|

| Interrupt Acknowledge       | 0000 |

| Special Cycle               | 0001 |

| I/O Read                    | 0010 |

| I/O Write                   | 0011 |

| Reserved                    | 0100 |

| Reserved                    | 0101 |

| Memory Read                 | 0110 |

| Memory Write                | 0111 |

| Reserved                    | 1000 |

| Reserved                    | 1001 |

| Configuration Read          | 1010 |

| Configuration Write         | 1011 |

| Memory Read Multiple        | 1100 |

| Dual Address Cycle          | 1101 |

| Memory Read Line            | 1110 |

| Memory Write and Invalidate | 1111 |

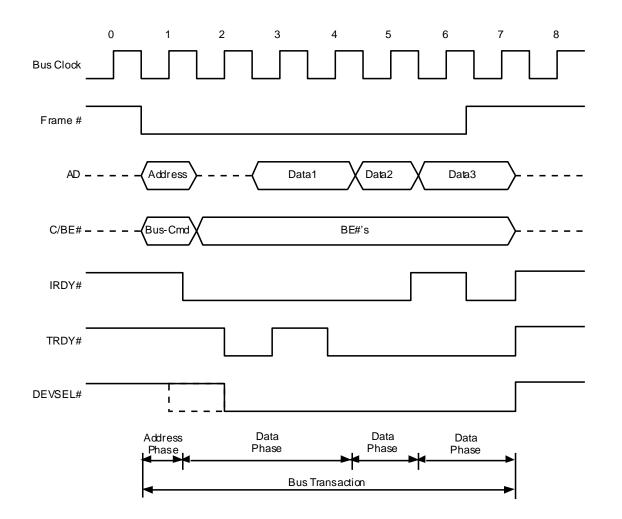

### **PCI Read Burst Cycle**

# **PCI Read Burst Cycle**

| Clock Cycle | Description of PCI operation                                                                                                                                                                                                                                                                                                                                         |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0           | Bus is idle                                                                                                                                                                                                                                                                                                                                                          |  |

| 1           | The initiator sets FRAME low, places the address on the Address/Data (AD <i>x</i> ) lines, and the bus command (read) on the Command/Byte Enable (C/BE) lines (address phase).                                                                                                                                                                                       |  |

| 2           | The initiator tri-states the address and waits for the target to return a data value by turning on its tri-state drivers. Device Select (DEVSEL) low indicates a target device has decoded its address range and it is responding to the command. The target drives TRDY high to indicate the target needs another clock cycle to respond with the data.(data phase) |  |

| 3           | The target drives the data value and sets target ready (TRDY) low to indicate that data is valid. When both IRDY and TRDY are low a data transfer occurs.                                                                                                                                                                                                            |  |

| 4           | The target sets TRDY high to indicate it need an additional clock cycle for the next data transfer.                                                                                                                                                                                                                                                                  |  |

| 5           | The second data transfer occurs when both TRDY and IRDY are low. The initiator saves the target data.                                                                                                                                                                                                                                                                |  |

| 6           | The target drives the data value, but the initiator requests an additional clock cycle by set IRDY high.                                                                                                                                                                                                                                                             |  |

| 7           | The initiator sets IRDY low to complete the third data transfer. The initiator saves the target data value, The initiator drives FRAME high to end the data phase.                                                                                                                                                                                                   |  |

| 8           | All bus signals are tri-stated or driven to the inactive state.                                                                                                                                                                                                                                                                                                      |  |

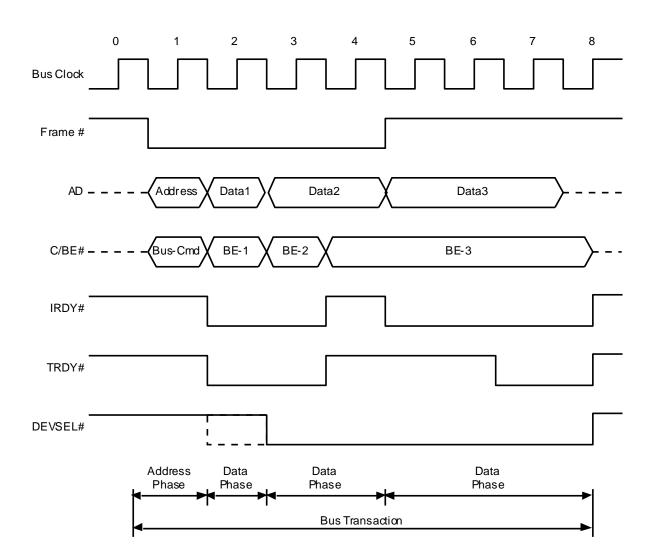

#### **PCI Write Burst Cycle**

# **PCI Write Burst Cycle**

| Clock Cycle | Description of PCI operation                                                                  |

|-------------|-----------------------------------------------------------------------------------------------|

| 0           | Bus is idle                                                                                   |

| 1           | The initiator sets FRAME low, places the address on the Address/Data (ADx) lines, and         |

|             | the bus command (write) on the Command/Byte Enable (C/BE) lines (address phase).              |

| 2           | The initiator places the data on the AD <i>x</i> lines and byte enables on C/BE lines, Device |

|             | Select (DEVSEL) low indicates a target device has decoded it's address range and it is        |

|             | responding to the command. When both IRDY and TRDY are low the target saves the               |

|             | data. (data phase)                                                                            |

| 3           | The initiator drives new data and byte enables. When both initiator ready IRDY and            |

|             | TRDY are low a data transfer occurs and the target saves the data.                            |

| 4           | The initiator sets IRDY high and the target sets TRDY requesting an additional clock          |

|             | cycle.                                                                                        |

| 5           | The initiator drives new data and byte enables and sets IRDY low. The initiator sets          |

|             | FRAME high indicating the final data transfer.                                                |

| 6           | The target drives the data value, but the initiator requests an additional clock cycle by     |

|             | set IRDY high.                                                                                |

| 7           | The initiator sets IRDY low to complete the third data transfer. The target saves the data    |

|             | value.                                                                                        |

| 8           | All bus signals are tri-stated or driven to the inactive state.                               |

# **Software for PCI devices**

- Each PCI device has a 256 byte configuration area

- At power up each device can respond with manufacturer and device type information

- Allows system to locate and load device drivers at power up

- Memory and I/O base addresses are configured with software (no jumpers)

# **Accelerated Graphics Port (AGP)**

- Newer Graphics cards were consuming most of the PCI bus bandwidth

- Solution: Move graphics card to its own PCI bus

- A connection with only 1 device is technically a "port" and not a "bus."

- Extra clock phase signals were added to increase clock rate 2X, 4X, and 8X

#### Logic Analyzer to capture PCI bus

| 🔛 PCI64X MVu | - <b>- - -</b>                                                                                               | <b>"</b> * | k ₽\$  & @   | 16 <b></b> 6 |                      | -   <b>H</b>   <b>+</b>   <b>C</b> E                     |                                       |

|--------------|--------------------------------------------------------------------------------------------------------------|------------|--------------|--------------|----------------------|----------------------------------------------------------|---------------------------------------|

|              | 1 🖬 🚮 🗲 🕅 → Time/Div: 50ns 🔽 🛒 🖓                                                                             | E          | 1:<br>DX54-2 | 0            | 12:<br>POIX64-2      | 0 📥 Delta Time: Os 📥                                     |                                       |

| C1: 50ns     | E2: 50ns Delta Time: 100ns                                                                                   |            | sample       | PCIX64       | PCIX64               | PCIX64<br>Mhemon1cs                                      | T1mestamp                             |

|              | 1 - 308.000 nz - 307.000 nz -                                                                                |            | 6            | 00000000     | F7FF0000             |                                                          | 44.431,000 us<br>30.000 ns            |

| Mag_Sample   |                                                                                                              | 11         |              |              | 06000008             | ATTRIBUTE CYCLE - DWORD<br>ND Snodp = Not Set            | 30.000 ns                             |

| Mag_AD_Hi    | 1A0D2228                                                                                                     | ш          |              |              | 06000008             | Relaxed Ordering = Not Set                               |                                       |

| Mag_AD_Lo    |                                                                                                              | ш          |              |              | 05000008             | Tag = Dx006 / 0d6<br>Reg. Bus #0x000 / 0d13              |                                       |

| Mag_Control  | FF00 XFF0A X FDFC XXX FF00                                                                                   | ш          |              |              | 05000008             | Red. Device #0x0D0 / Od0                                 |                                       |

| Mag_CLK      |                                                                                                              | ш          |              |              | 06000008             | Red. Function #0x000 / 0dD<br>Byte Enables - Bytes 3-0   |                                       |

| Mag_RST#     |                                                                                                              | ш          | 8            |              | 80140050             | SINGLE DATA PHASE DISCONNECT                             | 270.000 ns<br>180.000 ns              |

| Mag_REQ64#   |                                                                                                              | ш          | 10           | 00000000     | F7FF0000<br>070D0008 | MEMORY WRITE ADDRESS<br>ATTRIBUTE CYCLE - DWORD          | 30.000 ns                             |

| Mag_ACQ64#   |                                                                                                              | ш          | 10705.       |              | 07000008             | ND SNODD = NOT SET<br>Relaxed Ordering = Not Set         |                                       |

| Mag_FRAME#   |                                                                                                              | ш          |              |              | 07000008             | $Tag = D \times 007 / 0d7$                               |                                       |

| Mag_DEVSEL#  |                                                                                                              | ш          |              |              | 07000008             | Reg. Bus #0x00D / 0d13<br>Reg. Device #0x0D0 / 0d0       |                                       |

| Mag_STOP#    |                                                                                                              | ш          |              |              | 07000008             | Red. Eunction #0x000 / 0d0                               |                                       |

| Mag_IRDY#    | . Denotes lintered internal internal protect (it and a station recent internal internal internal internal if | ш          | 11           |              | 07000008             | Byte Enables - Bytes 3-0<br>SINGLE DATA PHASE DISCONNECT | 270,000                               |

| Mag_TRDY#    |                                                                                                              | ш          | 12           | 000000000    | F7FF0008             | MEMORY WRITE ADDRESS                                     | 270.000 ns<br>180.000 ns<br>30.000 ns |

| Mag_C/BE[7]# |                                                                                                              | ш          | 13           |              | 04000008             | ATTRIBUTE CYCLE - DWORD<br>ND SNODD - NOT SET            | 30.00D ns                             |

| Mag_C/BE[6]# |                                                                                                              | ш          |              |              | 04000008             | Relaxed Ordering = Not Set                               |                                       |

| Mag_C/BE[5]# |                                                                                                              | ш          |              |              | 04000008             | Relaxed Ordering = Not Set<br>Tag = 0x004 / 0d4          |                                       |

| Mag_C/BE[4]# |                                                                                                              |            |              |              | 04000008             | Req. Bus #0x00D / 0d13<br>Req. Device #0x0DD / 0d0       |                                       |

| Mag_C/BE[3]# |                                                                                                              |            |              |              | 04000008             | Req. Function #0x000 / 0dD                               |                                       |

| Mag_C/BE[2]# |                                                                                                              |            | 14           |              | 80F70050             | Byte Enables - Bytes 3-0<br>SINGLE DATA PHASE DISCONNECT | 270.000 ns                            |

| Mag_C/BE[1]# |                                                                                                              |            | 15           | 00000000     | F7FF0008             | MEMORY WRITE ADDRESS                                     | 180.000 ns                            |

| Mag_C/BE[0]# | المتحدين ومعيدة وميدور كبمين كبمين ومعييد مسطة محمد فمحد فمحد فسما المحد والمحد                              |            | 16           |              | 05000008             | ATTRIBUTE CYCLE - DWORD<br>No Snoop = Not Set            | 30.000 ns                             |

|              |                                                                                                              |            |              |              | 05000008             | Relaxed Ordering = Not Set                               | - I                                   |

|              |                                                                                                              |            | 14           |              | 1.01000008           |                                                          |                                       |

Figure 2.15 A Tektronix logic analyzer setup to capture and decode PCI bus signals. This logic analyzer is actually an embedded system that runs Windows XP. A special PCI interposer adapter card is used to quickly connect probes along with special firmware for the logic analyzer. Images courtesy of Nexus Technology.

| Comparing ISA/PCI   |                      |  |  |  |

|---------------------|----------------------|--|--|--|

| ISA                 | PCI                  |  |  |  |

| Adv:                |                      |  |  |  |

| 16 bits             | 32 bits              |  |  |  |

| slower              | faster               |  |  |  |

| separated addr/data | shared addr/data     |  |  |  |

| only PC system      | support many systems |  |  |  |

| simple protocol     | PCI bridge           |  |  |  |

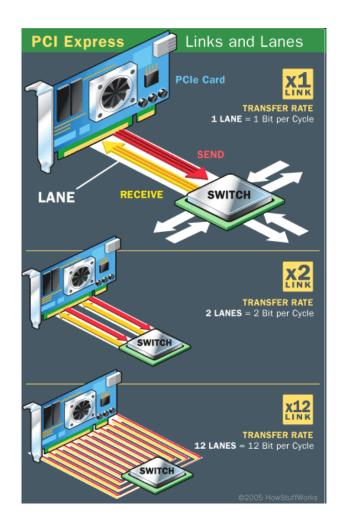

#### **Third Generation Bus – PCI Express**

- High-Speed Serial line(s) are used to transfer PCI signals

- Fewer signal lines are used, but with much higher bandwidth on each signal line

- More stringent design restrictions on drivers, length, loading, crosstalk, and terminations

- Clock rates from 2.5 Gbps to 10 Gbps

- Can combine serial lines into groups called lanes to provide more bandwidth to a device

- No changes needed in software works the same as PCI

## PCI-E speed

A lane is composed of a transmit and receive pairs of differential lines (4 wires)

Per lane:

**v1.x**: 250 MB/s

**v2.0**: 500 MB/s

**v3.0**: 1 GB/s

16 lane slot:

v1.x: 4 GB/s v2.0: 8 GB/s v3.0: 16 GB/s

#### **PCI-E** links and lanes

#### **PCI-E** connectors

#### **PCI Express** Example Connectors

#### BANDWIDTH

Single direction: 2.5 Gbps/200 MBps Dual Directions: 5 Gbps/400 MBps

#### BANDWIDTH

Single direction: 10 Gbps/800 MBps Dual Directions: 20 Gbps/1.6 GBps

**x8**

Source: IBM

INTERNATIONAL CONTRACTOR OF A STATE OF A STA CONTRACTOR DATA AND ADDRESS OF THE OWNER OWNER

COMPANY OF THE OWNER OF THE OWNER

CONTRACTOR DESCRIPTION OF THE OWNER OWNE

· monorement · monorement

CONTRACTOR OF TAXABLE

BANDWIDTH Single direction: 20 Gbps/1.6 GBps Dual Directions: 40 Gbps/3.2 GBps

MAMAMAN AND A STREET **x16** VINIMUM BANDWIDTH Single direction: 40 Gbps/3.2 GBps Dual Directions: 80 Gbps/6.4 GBps

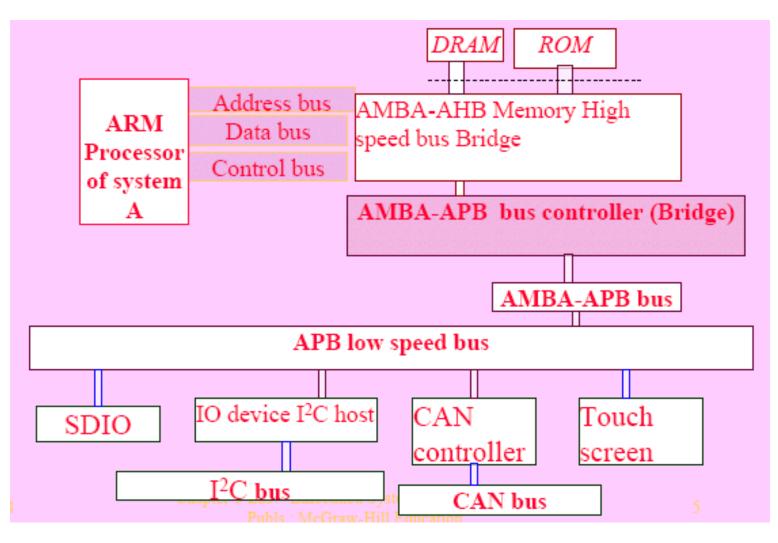

## ARM Bus

- Introduced by ARM Ltd in 1996

- Widely used as the on-chip bus

# ARM BUS

- AMBA = ARM Memory Bus Architecture

- AHB = ARM High performance Bus

- APB = ARM Peripheral Bus

- AMBA-AHB connects ARM core with memory, external DRAM

- AMBA-APB interfaces ARM core with external low-speed I/O devices using AMBA-APB bridge

# AMBA

- AMBA-AHB connects to 32-bit data and 32-bit address at high speed

- AHB maximum bps bandwidth is 16 times ARM processor clock

- AMBA-APB bridge is used to communicate AHB bus to APB bus

- The bridge communicates to memory through AMBA-AHB

### APB bus

#### Connect:

- I<sup>2</sup>C

- Touch screen

- SDIO

- MMC (multimedia-bus)

- USB

- CAN bus

## ARM BUS

# Logic analyzer to capture ARM instruction sequence

| P. X 🖻      |                      | AA                | 1 00 🕈               | Code                 |                                                          |                     |

|-------------|----------------------|-------------------|----------------------|----------------------|----------------------------------------------------------|---------------------|

| 205 -       | C2: 2                |                   | Delta Time           | -2.05us              | 🛨 🗖 Lock Delta Time                                      |                     |

| 0 -         | 80200                | 1                 |                      | - Co                 |                                                          |                     |

| Sample      | 80200<br>Address     | 80200<br>DRAMAddr | 80200<br>HiData      | 80200<br>LoData      | 80200<br>Mnemonics                                       | Timestamp           |

| 195         |                      | 003C              | A0008924             | A0008924             | / DESELECT )                                             | 10.500 ns           |

| 195         |                      | 0030              | A0008924<br>A0008924 | A0008924<br>A0008924 | ( DESELECT )                                             | 10.000 ns           |

| 190         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 198         |                      | 0036              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 199         |                      | 0036              | A0008924             | A0008924             | ( CAS READ )(SO~)                                        | 10.000 ns           |

| 200         |                      | 0038              | A0008924             | A0008924             | ( DESELECT ) [READ LATENCY]                              | 10.500 ns           |

| 201         | 00008980             | 0038              |                      | A000A784             | ANDGE R10, R0, R4, LSL 15                                | 10.000 ns           |

| 201         | 000089B4             | 0038              | A000A7A4             |                      | ANDGE R10, R0, R4, LSR 15                                | 10.000 113          |

| 202         | 000089B8             | 0038              |                      | A000A55C             | ANDGE R10, R0, R12, ASR R5                               | 10.000 ns           |

|             | 000089BC             | 0038              | A000A560             |                      | ANDGE R10, R0, R0, R0R 10                                |                     |

| 203         | 00008900             | 0038              |                      | 64697246             | STRVSBTR7, [R9], #-246                                   | 10.500 ns           |

| 0.258-02.0  | 000089C4             | 0038              | 00007961             |                      | ANDEQ R7, RO, R1, ROR 18                                 | and statement       |

| 204         | 000089C8             | 003C              |                      | 414051EC             | CMPMI R5, R0, R12, ROR 3                                 | 9.500 ns            |

| 0.258992530 | 000089CC             | 003C              | 41473333             |                      | CMPMI R3, R7, R3, LSR R3                                 | our cores.          |

| 205         | 000089D0             | 003C              |                      | 3FF00EA7             | SWICC/LO #FOOEA7                                         | 10.000 ns           |

| V2907003    | 000089D4             | 003C              | 24F27DB6             |                      | LDRCS/HSBTR7, [R2], #+DB6                                | and an and a second |

| 206         |                      | 003C              | E92DD831             | E1A0C00D             | ( DESELECT )[READ LATENCY]                               | 10.500 ns           |

| 207         | 0000000000000        | 003C              | E24DD034             | E28DB018             | ( DESELECT )                                             | 10.000 ns           |

| 208         |                      | 003C              | E24DD034             | E28DB018             | ( DESELECT )                                             | 10.000 ns           |

| 209         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 210         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 211         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.500 ns           |

| 212         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 213         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 214         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 215         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.500 ns           |

| 216         |                      | 003C              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 217         |                      | 0036              | A0008924             | A0008924             | ( DESELECT )                                             | 10.000 ns           |

| 218         |                      | 0036              | A0008924             | A0008924             | ( CAS READ )(SO~)                                        | 10.000 ns           |

| 219         |                      | 0038              | A0008924             | A0008924             | ( DESELECT ) [READ LATENCY]                              | 10.000 ns           |

| 220         | 000089B0             | 0038              |                      | A000A784             | ANDGE R10, R0, R4, LSL 15                                | 10.000 ns           |

|             | 000089B4             | 0038              | A000A7A4             |                      | ANDGE R10, R0, R4, LSR 15                                | 10.505              |

| 221         | 000089B8             | 0038              |                      | A000A55C             | ANDGE R10, R0, R12, ASR R5                               | 10.500 ns           |

|             | 000089BC             | 0038              | A000A560             | <br>C4C0724C         | ANDGE R10, R0, R0, R0R 10                                | 10,000,             |

| 222         | 000089C0<br>000089C4 | 0038              | 00007961             | 64697246             | STRVSBTR7, [R9], #-246                                   | 10.000 ns           |

|             |                      | 0038              |                      | 414051EC             | ANDEQ R7, RŎ, RÍ, ROR 18                                 | 10,000,             |

| 223         | 000089C8<br>000089CC | 003C<br>003C      | 41473333             | 414051EC             | CMPMI R5, R0, R12, R0R 3                                 | 10.000 ns           |

| 100         | 00008900             |                   | 41473333             | 3FF00EA7             | CMPMI R3, R7, R3, LSR R3<br>SWICC/LO #FOOEA7             | 10,000              |

| 224         | 000089D0             | 003C<br>003C      | 24F27DB6             | 3FF00EA/             |                                                          | 10.000 ns           |

| 225         | 00008904             | 0030              | 24F27DB6             | E1 40C000            | LDRCS/HSBTR7, [R2], #+DB6                                | 10.500 ns           |

| 225         | 000089D8             | 003C              | E92DD831             | E1A0C00D             | MOV R12, R0, R13<br>STMDB_R13!, R15,R14,R12,R11,R5,R4,R0 | 10.500 hs           |

**Figure 2.16** A Tektronix logic analyzer with optional software setup to capture and disassemble an ARM processor's instruction execution sequence. This logic analyzer is actually an embedded system

#### Other Bus interfaces

EISA bus

32 bit, asymmetric I/O channel

up to 33 MB/s data transfer rate

4GB address space, 8 DMA chanels

backward compatible with ISA

Futurebus+

Designed by IEEE896 committee 64 bit and 160 MB/s

#### Other Bus interfaces

- SCSI (small computer System Interface) bus ANSI standard 4MB – 10 MB per second data transfer rate mainly for computer to other devices, WIDE SCSI uses wider cable

- Ultra SCSI

Support from 20MB - 80 MB per second

• TURBO Channel bus

32 bit, asymmetric synchronous I/O channel 12.5 – 25 MHz data transfer rate Developed by DEC (digital)

## Other Bus interfaces

- XMI Bus

64 bits addressing

Upto 100 MB per second

- IEEE-796 (Multi-bus) introduced by Intel for multiprocessors on the same board, support 16 bit data and 24 bit address buses

#### VME bus (Euro standard) Similar to Intel Multi-bus, 24 bit address bus with 8/16/32 data buses

#### Questions?